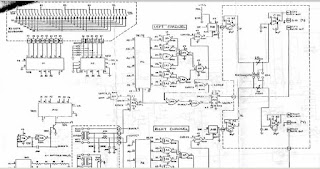

Although the schematics are easily found for the TVS-1, an actual circuit description of the digital keyboard circuitry is hard to locate. Having just fixed issues with this circuitry in two separate synthesizers, I decided to write my own. In case anyone else is crazy enough to delve into this and sort it all out, this could be useful information, even if incomplete.

There are four purposes to the digital keyboard circuitry: one is to provide the correct control voltage "cv", a voltage which will produce the correct frequency oscillation in the SEM module(pitch), the second produce is the "gate" voltage, a voltage which tells the SEM card that it is in use... enabling it to produce sound. The third purpose is to activate the sem cards in the right sequence (in unison, or right first and then left, etc). The fourth purpose is to astonish and stymie the repair technician with a brilliant, yet complex, array of logic gates.

The circuitry is designed to process two note polyphony, so after holding down one note, any second note played is sent to the other sem module.

This circuitry uses CMOS chips with a supply voltage of 9 volts... unlike many later logic chips (TTL) which only work with up to 5 volts.

1) the heartbeat of the circuit is A8, which is designed to produce a clock pulse which drives the other logic gates. It uses some RC components and a 4001 logic "or" gate. It's output, labeled "clock", should like like a clean square wave.

2)this "clock" pulse is routed to A8, a "counter" device which sequentially routes pulses among 6 outputs, labelled "a1 -a6".

3) These signals (a1-a6) from A8 are routed through a1, then the keyboard, then a2, which essentially produces a type of serial output which contains information about which keys were pressed. This output is shown in figure 1... it essentially is a serial synchronous data signal, which produces voltage spikes which reflect which of the 37 keys were pressed. Ultimately, these spikes lines up with the "dac" signal, and depending where the spike falls along the dac signal, an analog voltage is produced for EACH key that is pressed, these voltages are higher if the higher keys are pressed. Note that the voltage spikes are recurring, synchronous with the DAC signal, and thus line up in the same spot each time with with the recurrent dac signal, as long as the key is held. See figure 2.

4)Now the beauty of the design can be seen... an analog voltage for EACH key can be produced, and by manipulating the "dac" signal, you can make that voltage be higher or lower, or if necessary you can curve the dac signal slightly making the voltage difference across the keyboard non-linear.

5)the "dac" signal is produced using the outputs "a1-a6", by Ic's a16 and a17, and a series of resistors making a voltage "ladder"... an old fashioned "dac". The signal,when all is right, should be a 3 volt sawtooth as seen in figure 1 and 2. Conveniently, the signal can be modulated up and down by 3 volts by using the transpose switches, and adjusted using the trimmers on the board. The length of one "DAC" wave corresponds exactly to the time period of the output on the "data" rail.

6)It is useful to note here that any issues in the circuitry described thus far will produce intonation problems for BOTH left and right voices.... issues with the "clock" signal, the "dac" signal, or with the circuitry used to produce the "data" signal.

Most of the next section addresses the circuitry that effects each voice seperately.

7) "LGate and Rgate are signals which are either high or low, low signalling the "gate is open", and the voice is in use.

8) "RTAKEN and LTAKEN are signals which go High when the right or left voice is taken.

----

When a key is pressed on the keyboard, a voltage spike is present on the "data" signal. Let us suppose that left voice first is selected. In this case, A11 pin 12 and 13 will be high, allowing pin 11 to go low.

9) A12 pin 13 can now go High, which represents a clock pulse to latch A6.

10) The whole purpose of A6 and the network around it, is to "record" the position of the data pulse at that time of the key press, and to repeat it each DAC signal. A6 takes that recording when a12 pin 13 goes high, which moves the clock on the latch. After that, at each point when data lines a1-a6 are in that position, the network of logic gates a5,7,9, 8 and 11 will create a pulse which should line with the dac signal in the right position, so that the correct CV is produced by A18 pin 2. This voltage is stabilized by the small cap, and then run through op amp A6, which does not produce a voltage gain, but a current gain.

11) The gate is opened (goes low) on the first press of a key when a12 pin 13 goeshigh, a14 pin 4 goes low, then a15 pin 10 goes high. This, when synchronized with a data pulse at A14, causes a14 pin 12 to go low (and a14 pin 13 to go high. This happens at the first keypress, and initially opens the gate. After that, A15 pin 11 goes high with each successive DAC cycle,a15 pin 4 goes low, and a15pin 10 goes high. and as long as there is a concurrent data pulse at 14 pin 9 (ie the key is held down), L gate stays open, and a sound is played from the left SEM. when the key is let up, the data pulse is no longer present at pin 9, and the gate is allowed to go high again. now a11 pin 13 is high, and the process can start again.

The process is essentially mirrored on the circuitry which corresponds to the Right Gate.

========================

Some other things:

Some issues with a weak resonance effect in the VCO's came down to a weak 3080, a transconductance op amp.

The customer was also concerned about driving the sequencer with an external clock,which did not produce the correct voltage for the TVS logic... for example a standard TTL square wave, from a 5 volt clock, may not drive the TVS CMOS logic chips properly.These chips are designed to see logic highs above 7 volts (see http://www.allaboutcircuits.com/vol_4/chpt_3/10.html). Thus in the signal path between an external clock jack which I installed, I added the small circuit below, which was effective in buffering the external clock input, and allowing it to accept a wide range of voltages. The second transistor is added to make the output square wave in phase with the input (as the first stage turns it upside down). The high value collector resistors mean that the circuit wont draw much current... you may notice it is not a wonderfully designed amplifier circuit, and more biasing could be done... however the transistors are either off or completely saturated, so I think all that extra biasing would be unnecessary.

Great work. Thanks for your time and another brilliant article on digital keyboard.

ReplyDeleteIC Design